## TC220C/E DRAM Core

0.3µm 3T dRAMASIC

## Embedded DRAM Benefits

Benefits derived from integration of DRAM with logic are:

- Flexibility in utilizing different DRAM core configurations based on the application requirement

- Memory access time lower than discrete packaged devices

- Elimination of a large number of pins and associated packages, effectively reducing circuit board area

- Lower power consumption since systems with fast and wide memory busses will dissipate significantly less power due to lower capacitance on-chip connections

- · Lower switching noise on data bus between memory and logic

### **Target Applications**

Applications for 3T dRAMASIC<sup>™</sup> include hard disk drive controllers, buffer memory for hubs and switches and printers.

Toshiba's 1 Mbit embedded DRAM core is available for the

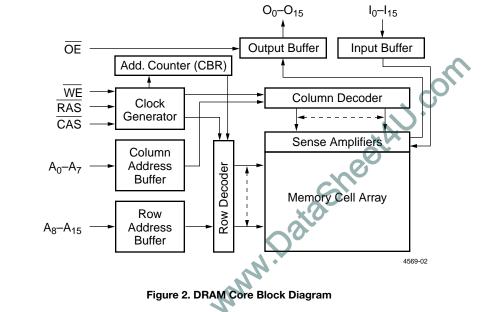

# DRAM Core Features

- Power supply: 3.3V ±0.3V

- Memory configurations

- 128K x 8 bit

- 64K x 16 bit

- 32K x 32 bit

- 16K x 64 bit

- · Full address without multiplex

- Separate data input and output

- Read access modes

- Random access

- EDO/Hyper page mode

- Refresh scheme

- RAS only refresh

- CBR ( $\overline{CAS}$  before  $\overline{RAS}$ ) refresh

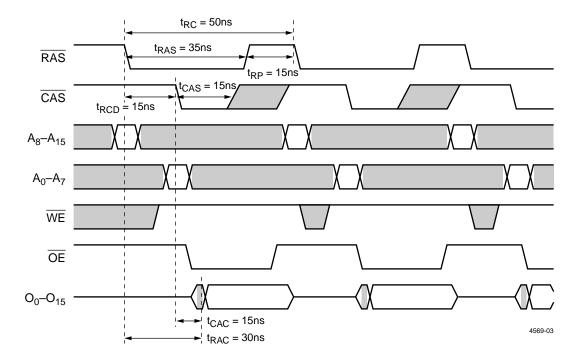

- Performance specification

- trc random read cycle: 50 ns

- tpc page mode read cycle: 25 ns

- Refresh cycle: 256 cycles/ms (@Tj =  $85^{\circ}$ C)

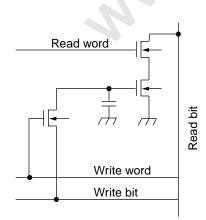

Figure 1. Three-Transistor DRAM Cell

#### **Timing Diagrams**

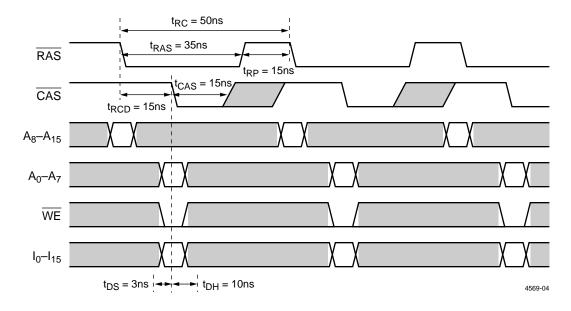

Figure 4. Random Mode Write Cycle

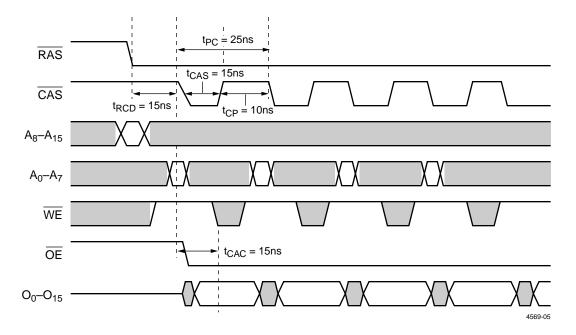

Figure 5. Hyper Page Mode Read Cycle

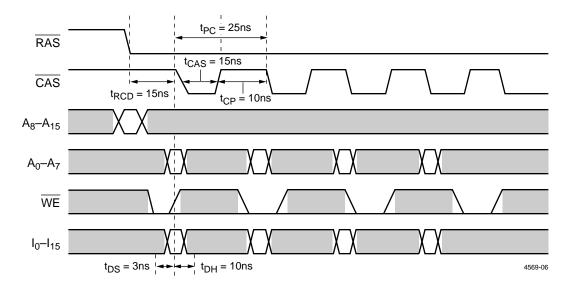

Figure 6. Hyper Page Mode Write Cycle

#### **Technology Resource Centers**

Toshiba ASIC Technology Resource Centers are located throughout the U.S. and provide a high level of technical expertise for support before, during and after the design of a Toshiba ASIC. This includes support issues dealing with EDA environments and design kits, Toshiba design methodologies, Toshiba ASIC technologies and Toshiba ASIC design implementation. Design consultation is also available.

In addition, Toshiba's North America Semiconductor Engineering Development Center in San Jose, CA is staffed by system, technology and EDA design experts to work with partners on advanced System IC applications.

Rigorous production quality control and monitoring coupled with a sophisticated batch tracking system enables Toshiba to meet the requirements of fast ramping, high volume markets.

#### www.toshiba.com/taec

1. This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

The information in this document has been carefully checked and is believed to be reliable; however, no responsibility can be assumed for inaccuracies that may not have been caught. All information in this document is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

#### TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

#### **Regional Sales Offices**

**Irvine, CA** TEL: (714) 453-0224 FAX: (714) 453-0125

**San Jose, CA** TEL: (408) 456-8900 FAX: (408) 456-8910 **Atlanta, GA** TEL: (770) 931-3363 FAX: (770) 931-7602

**Chicago, IL** TEL: (708) 945-1500 FAX: (708) 945-1044 **Boston, MA** TEL: (617) 224-0074 FAX: (617) 224-1096

**Edison, NJ** TEL: (908) 248-8070 FAX: (908) 248-8030 **Portland, OR** TEL: (503) 629-0818 FAX: (503) 629-0827

**Dallas, TX** TEL: (972) 480-0470 FAX: (972) 235-4114

AS31950497